Microcontroller Atmel ATmega2564 8bit AVR

Features

- Supportu di a rete da hardware assistitu Filtru di l'indirizzi PAN multiplici

- Hardware avanzatu assistitu cunsumu d'energia ridutta

- Microcontroller AVR® 8-Bit High Performance, Low Power

- Architettura avanzata RISC

- 135 Istruzzioni putenti - A maiò parte di l'esecuzione di u ciclu di l'orologio unicu

- 32 × 8 Registri di travagliu generale per u scopu / Multiplicatore di 2 cicli On-Chip

- Finu à 16 MIPS Throughput à 16 MHz è 1.8 V - Funzionamentu cumpletamente staticu

- Programma non volatile è Memorie di Dati

- 256K/128K/64K Bytes di Flash Autoprogrammable In-System

- Endurance: 10'000 cicli di scrittura/cancellazione @ 125 °C (25'000 cicli @ 85 °C)

- 8K/4K/2K Bytes EEPROM

- Endurance: 20'000 cicli di scrittura/cancellazione @ 125 °C (100'000 cicli @ 25 °C)

- SRAM interna 32K/16K/8K Bytes

- JTAG (IEEE std. 1149.1 compliant) Interfaccia

- Capacità di scansione di cunfini Sicondu u JTAG Standard

- Amplitu Supportu di Debug On-chip

- Programmazione di Flash EEPROM, Fuses and Lock Bits through the JTAG interfaccia

- Funzioni periferiche

- Multiple Timer / Counter è canali PWM

- Contatore in tempu reale cù oscillatore separatu

- 10-bit, 330 ks/s Convertitore A/D; Comparatore Analogicu; Sensore di temperatura in chip

- Interfaccia seriale SPI Master/Slave

- Dui USART seriali programmabili

- Interfaccia seriale à 2 fili orientata à i byte

- Gestione avanzata di interruzioni è Modi di risparmiu di energia

- Watchdog Timer cù Oscillatore On-Chip Separatu

- Reset di putenza è Rilevatore di Brown-Out di corrente bassa

- Transceiver di bassa putenza cumplettamente integratu per a banda ISM 2.4 GHz

- High Power Ampsupportu di lifier da a suppressione di lobi laterali di spettru TX

- Velocità di dati supportati: 250 kb/s è 500 kb/s, 1 Mb/s, 2 Mb/s

- -100 dBm Sensibilità RX; Potenza di Output TX finu à 3.5 dBm

- MAC Assistitu da Hardware (Ricunniscenza Auto, Retry Auto)

- 32 Bit IEEE 802.15.4 Symbol Counter

- SFD-Detection, Spreading; De-Spreading; Inquadramentu ; CRC-16 Computazione

- Diversità d'antenna è cuntrollu TX / RX / TX / RX 128 Byte Frame Buffer

- sintetizzatore PLL cù spaziatura di canali 5 MHz è 500 kHz per a banda ISM 2.4 GHz

- Sicurezza Hardware (AES, True Random Generator)

- Oscillatori di Cristalli Integrati (32.768 kHz & 16 MHz, cristallu esternu necessariu)

- I/O è pacchettu

- 33 Linee I/O programmabili

- 48-pad QFN (RoHS/Fully Green)

- Gamma di temperatura: -40 ° C à 125 ° C industriale

- Cunsumu Ultra Low Power (1.8 à 3.6V) per AVR & Rx/Tx: 10.1mA/18.6 mA

- Modu attivu CPU (16MHz): 4.1 mA

- Transceiver 2.4 GHz: RX_ON 6.0 mA / TX 14.5 mA (potenza massima di uscita TX)

- Modu di sonnu profondu: <700nA @ 25 ° C

- Grade di Velocità: 0 - 16 MHz @ 1.8 - 3.6V gamma cù u vol integratutage regulatori

Applicazioni

- ZigBee®/ IEEE 802.15.4-2011/2006/2003™ - Dispositivu di funzione cumpleta è ridotta

- Transceiver di Banda ISM 2.4GHz per scopi generale cù Microcontroller

- RF4CE, SP100, WirelessHART™, Applicazioni ISM è IPv6 / 6LoWPAN

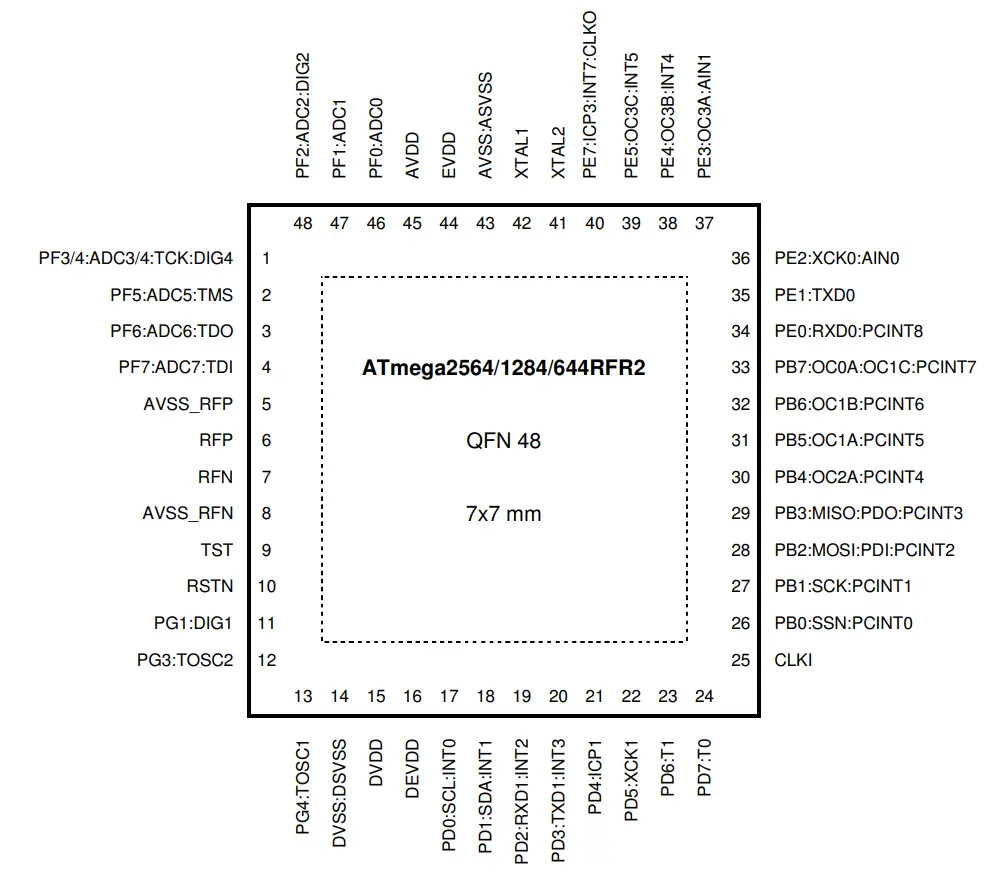

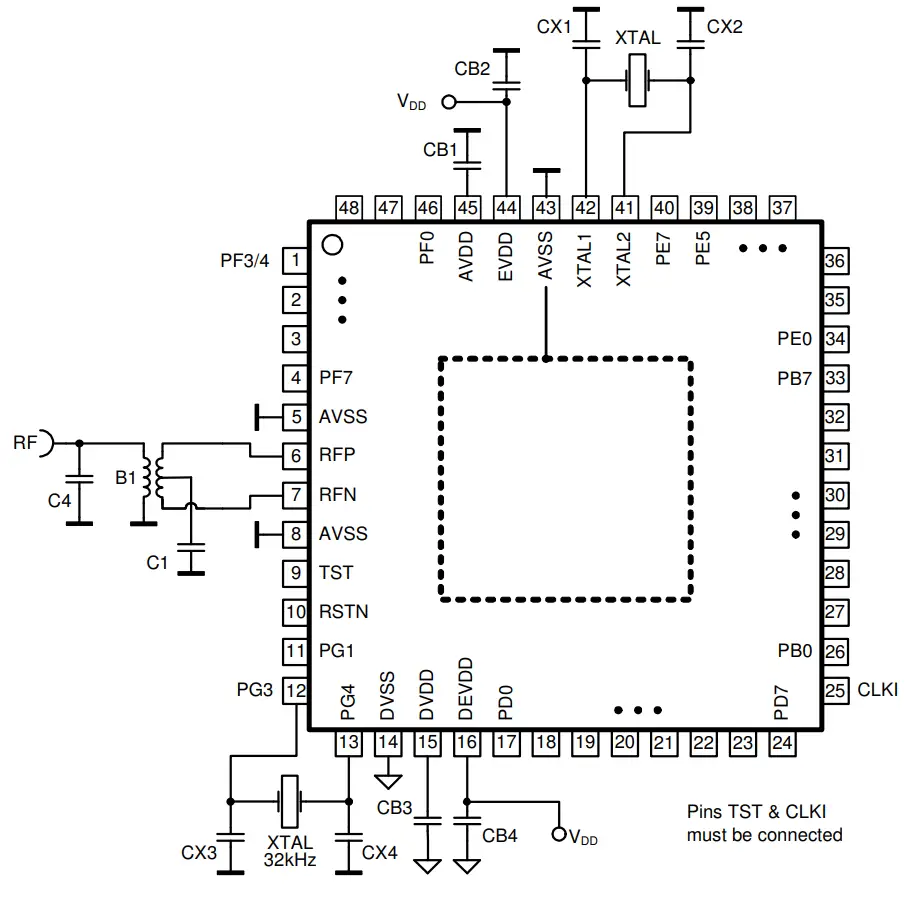

Configurazioni Pin

Figura 1-1. Pinout ATmega2564/1284/644RFR2

Nota: U grande pad centrale sottu à u pacchettu QFN / MLF hè fattu di metallu è internamente cunnessu à AVSS. Deve esse saldatu o pegatu à u bordu per assicurà una bona stabilità meccanica. Se u pad cintrali ùn hè micca cunnessu, u pacchettu pò alluntanassi da u bordu. Ùn hè cunsigliatu di utilizà a paleta esposta cum'è un sustitutu di i pin AVSS regularmente.

Disclaimer

I valori tipici cuntenuti in questa datasheet sò basati nantu à i risultati di simulazione è di carattarizazione di altri microcontrollers AVR è transceivers radio fabbricati in una tecnulugia di prucessu simili. I valori minimi è massimi seranu dispunibili dopu chì u dispusitivu hè carattarizatu.

Overview

L'ATmega2564/1284/644RFR2 hè un microcontroller CMOS di 8-bit di bassa putenza basatu annantu à l'architettura RISC avanzata AVR cumminata cù un transceiver di alta velocità di dati per a banda ISM 2.4 GHz.

Eseguendu struzzioni putenti in un unicu ciclu di clock, u dispusitivu ottene throughputs chì avvicinanu 1 MIPS per MHz chì permettenu à u designer di u sistema di ottimisà u cunsumu di energia versus a velocità di trasfurmazioni.

U transceiver radio furnisce alta velocità di dati da 250 kb/s à 2 Mb/s, gestione di frames, sensibilità eccezziunale di u receptore è una putenza di trasmissione elevata chì permette una cumunicazione wireless assai robusta.

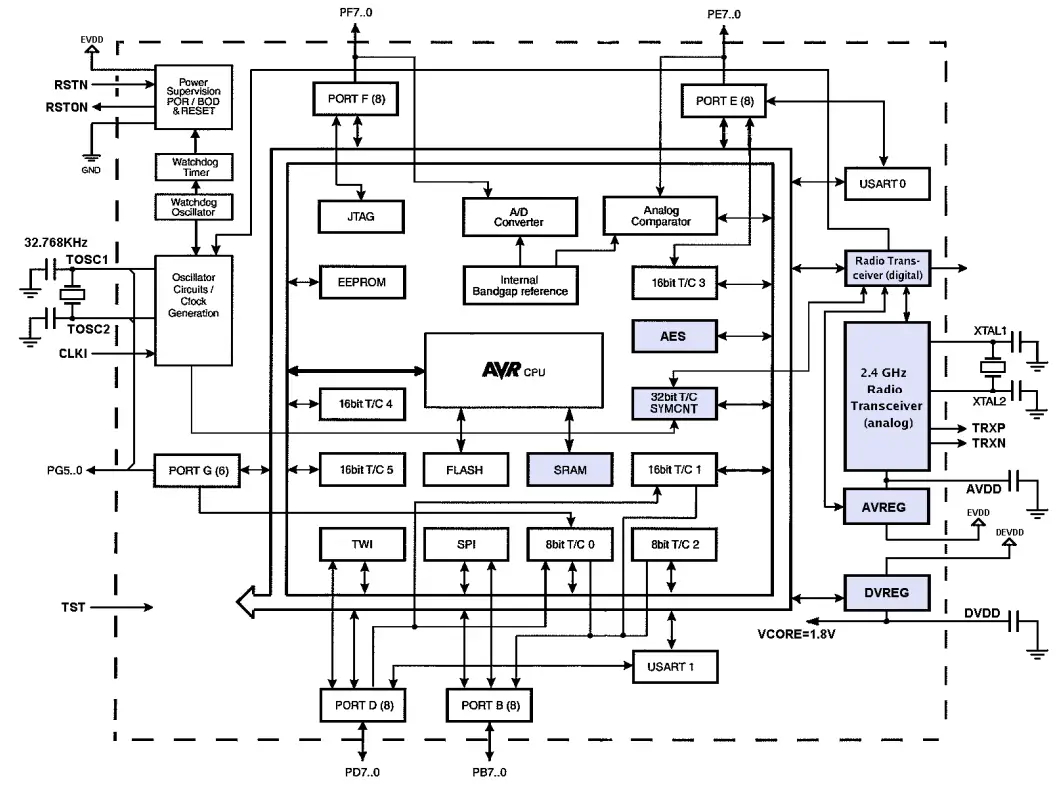

Diagramma di Blocu

Figura 3-1 Block Diagram

U core AVR combina un riccu set di struzzioni cù 32 registri di travagliu generale. Tutti i 32 registri sò direttamente cunnessi à l'Unità Logica Aritmetica (ALU). Dui registri indipendenti ponu accede cù una sola istruzzione eseguita in un ciclu di clock. L'architettura risultante hè assai còdice efficiente mentre ghjunghje à throughputs finu à deci volte più veloce di i microcontroller CISC convenzionali. U sistema include vol internutage regulazione è una gestione avanzata di putenza. Distinguitu da a piccula corrente di fuga permette un tempu di operazione prolongatu da a batteria.

U transceiver radio hè una suluzione ZigBee cumplettamente integrata chì utilizeghja un numeru minimu di cumpunenti esterni. Unisce un rendimentu RF eccellenti cù un costu bassu, una piccula dimensione è un bassu cunsumu di corrente. U transceiver radio include un sintetizzatore, trasmettitore è ricevitore frazionariu-N stabilizatu in cristalli, è un processu cumpletu di Sequenza Diretta Spread Spectrum Signal (DSSS) cù diffusione è despreading. U dispusitivu hè cumplettamente compatible cù i normi IEEE802.15.4-2011/2006/2003 è ZigBee. L'ATmega2564/1284/644RFR2 furnisce e seguenti caratteristiche: 256K/128K/64K Bytes di Flash Programmable In-System (ISP) cù capacità di lettura mentre scrive, 8K/4K/2K Bytes EEPROM, 32K/16K/8K Bytes SRAM, finu à 35 linee I/O di scopu generale, 32 registri di travagliu generale, Contatore in tempu reale (RTC), 6 Timer / Contatori flessibili cù modi di paragone è PWM, un Timer / Contatore di 32 bit, 2 USART, un byte orientatu à 2 fili Interfaccia seriale, un convertitore analogicu à digitale (ADC) à 8 canali, 10 bit cù un input differenziale opzionale.tage cun guadagnu programabile, Timer Watchdog programmabile cù Oscillatore Internu, un portu seriale SPI, IEEE std. Conforme à 1149.1 JTAG interfaccia di prova, ancu utilizata per accede à u sistema di Debug On-chip è a prugrammazione è 6 modi di risparmiu di energia selezziunati da u software.

U modu Idle ferma u CPU mentre permette à a SRAM, Timer / Counters, u portu SPI è u sistema di interruzzione per cuntinuà à funziunà. U modu Power-down salva u cuntenutu di u registru ma congela l'Oscillator, disattivendu tutte e altre funzioni di chip finu à a prossima interruzzione o reset hardware. In u modu di risparmiu di energia, u timer asincronu cuntinueghja à curriri, chì permette à l'utilizatori di mantene una basa di timer mentre u restu di u dispusitivu dorme. U modu di Riduzzione di Rumore ADC ferma u CPU è tutti i moduli I/O eccettu u timer asincronu è ADC, per minimizzà u rumore di cambiamentu durante e cunversione ADC. In u modu Standby, l'oscillatore RC funziona mentre u restu di u dispusitivu dorme. Questu permette un start-up assai veloce cumminatu cù un bassu cunsumu d'energia. In u modu di Standby Extended, l'oscillatore RC principale è u timer asincronu cuntinueghjanu à correre.

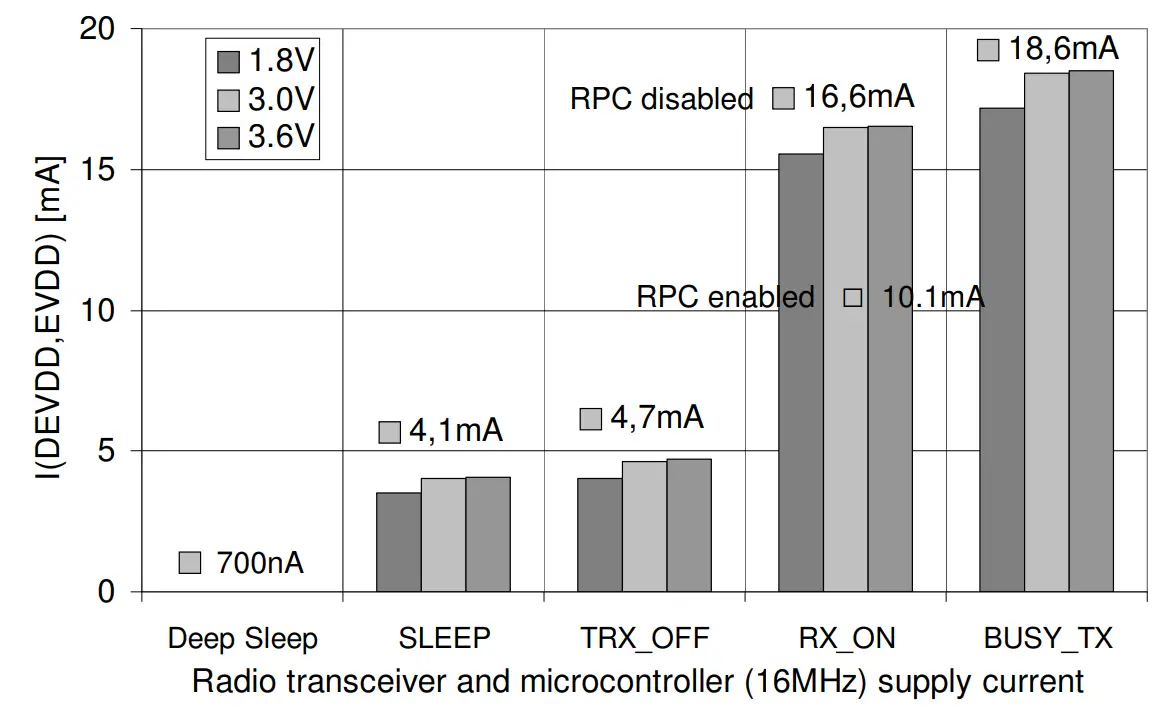

A currente di fornitura tipica di u microcontroller cù u clock CPU impostatu à 16MHz è u transceiver radio per i stati più impurtanti hè mostratu in a Figura 3-2 sottu.

Figura 3-2 Transceiver radio è microcontroller (16MHz) supply current

A putenza di uscita di trasmissione hè stabilita à u massimu. Se u transceiver radio hè in modu SLEEP, u currente hè dissipatu solu da u microcontroller AVR.

In u modu Deep Sleep, tutti i blocchi digitali maiò senza esigenze di ritenzione di dati sò scollegati da l'alimentazione principale chì furnisce una corrente di fuga assai chjuca. Watchdog timer, contatore di simbulu MAC è oscillatore 32.768kHz ponu esse cunfigurati per cuntinuà à curriri.

U dispusitivu hè fabricatu cù a tecnulugia di memoria non volatile d'alta densità di Atmel.

L'ISP Flash On-chip permette à a memoria di u prugramma esse riprogrammata in u sistema attraversu una interfaccia seriale SPI, da un programatore di memoria non volatile convenzionale, o da un prugramma di boot in chip in esecuzione in u core AVR. U prugramma di boot pò utilizà qualsiasi interfaccia per scaricà u prugramma di l'applicazione in a memoria Flash di l'applicazione.

U software in a sezione Flash di boot continuerà à eseguisce mentre a sezione Flash di l'applicazione hè aghjurnata, furnisce una vera operazione Read-While-Write. Cumminendu un CPU RISC di 8 bit cù Flash Auto-Programmable In-System in un chip monoliticu, l'Atmel ATmega2564/1284/644RFR2 hè un putente microcontrollore chì furnisce una soluzione altamente flessibile è efficae in costu à parechje applicazioni di cuntrollu integrate.

L'ATmega2564/1284/644RFR2 AVR hè supportatu cù una suite completa di prugrammi è strumenti di sviluppu di u sistema cumpresi: compilatore C, assemblatori macro, debugger / simulatori di prugramma, emulatori in-circuit, è kit di valutazione.

Descrizioni Pin

EVDD

Fornitura analogica esterna voltage.

DEVDD

Fornitura digitale esterna voltage.

Avddd

Fornitura analogica regulata voltage (generatu internamente).

DVDD

Fornitura digitale regulata voltage (generatu internamente).

DVSS

Terra digitale.

AVSS

Terra analogica.

Portu B (PB7…PB0)

U portu B hè un portu I/O bidirezionale di 8 bit cù resistori di pull-up interni (scelti per ogni bit). I buffer di output di Port B anu caratteristiche di unità simmetriche cù una capacità elevata di lavamanu è di fonte. Cum'è inputs, i pins di Port B chì sò esterni tirati bassu surghjeranu corrente se i resistori di pull-up sò attivati. I pins Port B sò tri-stated quandu una cundizione di resettore diventa attivu, ancu s'è u clock ùn hè micca in esecuzione.

Port B furnisce ancu funzioni di diverse caratteristiche speciale di l'ATmega2564/1284/644RFR2.

Port D (PD7…PD0)

Port D hè un portu I/O bidirezionale di 8 bit cù resistori di pull-up interni (scelti per ogni bit). I buffer di output Port D anu caratteristiche di unità simmetriche cù una capacità elevata di lavamanu è di fonte. Cum'è inputs, i pins di Port D chì sò esterni tirati bassu surghjeranu corrente se i resistori di pull-up sò attivati. I pins Port D sò tri-stated quandu una cundizione di resettore diventa attiva, ancu s'è u clock ùn hè micca in esecuzione.

Port D furnisce ancu funzioni di diverse caratteristiche speciale di l'ATmega2564/1284/644RFR2.

Port E (PE7,PE5...PE0)

Internamente Port E hè un portu I/O bidirezionale di 8 bit cù resistori di pull-up interni (scelti per ogni bit). I buffer di output Port E anu caratteristiche di unità simmetriche cù una capacità elevata di lavamanu è di fonte. Cum'è inputs, i pins Port E chì sò esterni tirati bassu surghjeranu currente se i resistori pull-up sò attivati. I pins Port E sò tri-stated quandu una cundizione riiniziata diventa attivu, ancu s'è u clock ùn hè in esecuzione.

A causa di u bassu pin count di u pacchettu QFN48 portu E6 ùn hè micca cunnessu à un pin. Port E furnisce ancu e funzioni di diverse funziunalità particulari di l'ATmega2564/1284/644RFR2.

Port F (PF7..PF5,PF4/3,PF2…PF0)

Internamente Port F hè un portu I/O bidirezionale di 8 bit cù resistori di pull-up interni (scelti per ogni bit). I buffer di output Port F anu caratteristiche di unità simmetriche cù una capacità elevata di lavamanu è di fonte. Cum'è inputs, i pins Port F chì sò esterni tirati bassu surghjeranu corrente se i resistori di pull-up sò attivati. I pins Port F sò tri-stated quandu una cundizione di resettore diventa attiva, ancu s'è u clock ùn hè micca in esecuzione.

A causa di u bassu pin count di u pacchettu QFN48 portu F3 è F4 sò cunnessi à u listessu pin. A cunfigurazione I/O deve esse fatta cù cura per evità una dissipazione eccessiva di putenza.

Port F furnisce ancu funzioni di diverse caratteristiche speciale di l'ATmega2564/1284/644RFR2.

Port G (PG4,PG3,PG1)

Internamente Port G hè un portu I/O bidirezionale di 6 bit cù resistori di pull-up interni (scelti per ogni bit). I buffer di output Port G anu caratteristiche di unità simmetriche cù una capacità elevata di lavamanu è di fonte. Tuttavia, a forza di u driver di PG3 è PG4 hè ridutta cumparatu cù l'altri pin di portu. L'output voltage drop (VOH, VOL) hè più altu mentre u currente di fuga hè più chjucu. Cum'è inputs, i pins Port G chì sò esterni tirati bassu surghjeranu currente se i resistori pull-up sò attivati. I pins Port G sò tri-stated quandu una cundizione di resettore diventa attivu, ancu s'è u clock ùn hè micca in esecuzione.

A causa di u bassu pin count di u portu di pacchettu QFN48 G0, G2 è G5 ùn sò micca cunnessi à un pin.

Port G furnisce ancu e funzioni di diverse caratteristiche speciale di l'ATmega2564/1284/644RFR2.

AVSS_RFP

AVSS_RFP hè un pin di terra dedicatu per u portu I/O RF bidirezionale è differenziale.

AVSS_RFN

AVSS_RFN hè un pin di terra dedicatu per u portu I/O RF bidirezionale è differenziale.

RFP

RFP hè u terminal pusitivu per u portu I/O RF bidirezionale è differenziale.

RFN

RFN hè u terminal negativu per u portu I/O RF bidirezionale è differenziale.

RSTN

Resetta l'input. Un livellu bassu nantu à questu pin per più di a durata minima di l'impulsu generarà un reset, ancu s'ellu ùn hè micca in esecuzione. I impulsi più brevi ùn sò micca garantiti per generà un reset.

XTAL1

Ingressu à l'oscillatore à cristallo inversu 16MHz amplificatore. In generale, un cristallu trà XTAL1 è XTAL2 furnisce u clock di riferimentu 16MHz di u transceiver radio.

XTAL2

Sortie di l'oscillatore à cristallo inversu di 16 MHz amppiù vivu.

TST

U modu di prugrammazione è di prova attivanu u pin. Se u pin TST ùn hè micca usatu tirallu à bassu.

CLKI

Ingressu à u sistema di clock. Se sceltu, furnisce u clock di u microcontroller.

Pins inutilizati

I pin flottanti ponu causà dissipazione di putenza in l'input digitale stage. Deve esse cunnessi à una fonte adatta. In i modi di funziunamentu normale, i resistori di pull-up interni ponu esse attivati (in Reset tutti i GPIO sò cunfigurati cum'è input è i resistori di pull-up ùn sò micca attivati).

I pin I/O bidirezionali ùn sò micca cunnessi à a terra o à l'alimentazione direttamente.

I pins di input digitale TST è CLKI devenu esse cunnessi. Se u pin TST inutilizatu pò esse cunnessu à AVSS mentre CLKI deve esse cunnessu à DVSS.

I pins di output sò guidati da u dispusitivu è ùn float. I pins di l'alimentazione di l'alimentazione sò cunnessi inseme internamente.

XTAL1 è XTAL2 ùn anu mai esse forzatu à furnisce voltagè à u listessu tempu.

Compatibilità è Limitazioni di Funzioni di u Pacchettu QFN-48

AREF

A riferenza voltagL'output di u convertitore A/D ùn hè micca cunnessu à un pin in l'ATmega2564/1284/644RFR2.

Portu E6

U portu E6 ùn hè micca cunnessu à un pin in l'ATmega2564/1284/644RFR2. E funzioni di pin alternativu cum'è input di clock à u timer 3 è l'interruzzione esterna 6 ùn sò micca dispunibili.

Port F3 è F4

U portu F3 è F4 sò cunnessi à u listessu pin in l'ATmega2564/1284/644RFR2. A cunfigurazione di output deve esse fatta cù cura per evità u cunsumu di corrente eccessiva.

A funzione di pin alternata di u portu F4 hè aduprata da u JTAG interfaccia. Se u JTAG L'interfaccia hè aduprata u portu F3 deve esse cunfiguratu cum'è input è l'output di funzione pin alternata DIG4 (indicatore RX / TX) deve esse disattivatu. Altrimenti, JTAG l'interfaccia ùn funziona micca. U SPIEN Fuse deve esse programatu per pudè sguassà un prugramma chì accidintali cunduce u portu F3.

Ci hè solu 7 canali di input unicu à l'ADC dispunibili.

Portu G0

U portu G0 ùn hè micca cunnessu à un pin in l'ATmega2564/1284/644RFR2. A funzione alternata di pin DIG3 (indicatore RX / TX invertitu) ùn hè micca dispunibule. Se u JTAG L'interfaccia ùn hè micca aduprata a funzione di pin alternata DIG4 di u portu F3 pò ancu esse usata cum'è indicatore RX / TX.

Portu G2

U portu G2 ùn hè micca cunnessu à un pin in l'ATmega2564/1284/644RFR2. A funzione alternata di pin AMR (input di lettura automatica asincrona à u timer 2) ùn hè micca dispunibule.

Portu G5

U portu G5 ùn hè micca cunnessu à un pin in l'ATmega2564/1284/644RFR2. A funzione di pin alternata OC0B (canale di comparazione di output di timer 8-Bit 0) ùn hè micca dispunibule.

RSTON

L'uscita di reset RSTON chì signala u statu di reset internu ùn hè micca cunnessu à un pin in l'ATmega2564/1284/644RFR2.

Riassuntu di cunfigurazione

Sicondu i requisiti di l'applicazione, una dimensione di memoria variabile permette di ottimisà u cunsumu di corrente è a corrente di fuga.

Tabella 3-1 Configurazione di Memoria

| Dispositivu | Flash | EEPROM | SRAM |

| ATmega2564RFR2 | 256 KB | 8 KB | 32 KB |

| ATmega1284RFR2 | 128 KB | 4 KB | 16 KB |

| ATmega644RFR2 | 64 KB | 2 KB | 8 KB |

U pacchettu è a cunfigurazione di pin assuciata sò listessi per tutti i dispositi chì furniscenu funziunalità cumpleta à l'applicazione.

Tabella 3-2 Configurazione di u Sistema

| Dispositivu | Pacchettu | GPIO | Serial IF | Canale ADC |

| ATmega2564RFR2 | QFN48 | 33 | 2 USART, SPI, TWI | 7 |

| ATmega1284RFR2 | QFN48 | 33 | 2 USART, SPI, TWI | 7 |

| ATmega644RFR2 | QFN48 | 33 | 2 USART, SPI, TWI | 7 |

I dispositi sò ottimizzati per l'applicazioni basate nantu à a specificazione ZigBee è IEEE 802.15.4. Avè una pila d'applicazioni, una strata di rete, una interfaccia di sensori è un cuntrollu di putenza eccellente cumminatu in un unicu chip parechji anni di operazione deve esse pussibule.

Table 3-3 Application Profile

| Dispositivu | Applicazione |

| ATmega2564RFR2 | Grande Coordinatore di Rete / Router per IEEE 802.15.4 / ZigBee Pro |

| ATmega1284RFR2 | Coordinatore di rete / Router per IEEE 802.15.4 |

| ATmega644RFR2 | Dispositivu di nodu finale / processore di rete |

Circuiti d'applicazione

Schema di l'applicazione di basa

Un schema di l'applicazione basica di l'ATmega2564/1284/644RFR2 cù un connettore RF unicu hè mostratu in a Figura 4-1 sottu è a Bill of Material associata in a Tabella 4-1 in a pagina 10. L'entrata RF 50Ω single-ended hè trasfurmata. à l'impédance différentielle du port RF de 100 Ω en utilisant Balun B1. I condensatori C1 è C2 furniscenu l'accoppiamentu AC di l'input RF à u portu RF, u condensatore C4 migliora l'abbinamentu.

Figura 4-1. Schema di l'applicazione basica (pacchettu 48 pin)

I condensatori di bypass di l'alimentazione (CB2, CB4) sò cunnessi à u pin di alimentazione analogica esterna (EVDD, pin 44) è u pin di fornitura digitale esterna (DEVDD, pin 16). U condensatore C1 furnisce l'accoppiamentu AC necessariu di RFN / RFP.

I pin flottanti ponu causà una dissipazione eccessiva di putenza (per esempiu durante l'accensione). Deve esse cunnessi à una fonte adatta. GPIO ùn deve esse cunnessu à a terra o à l'alimentazione direttamente.

I pins di input digitale TST è CLKI devenu esse cunnessi. Se u pin TST ùn serà mai usatu, pò esse cunnessu à AVSS mentre chì un pin CLKI inutilizatu puderia esse cunnessu à DVSS (vede u capitulu "Pin inutilizati").

I condensatori CB1 è CB3 sò capacitori di bypass per u volu analogicu è digitale integratutage regulatori per assicurà un funziunamentu stabile è per migliurà l'immunità di u rumore.

Condensatori deve esse piazzatu u più vicinu pussibule à i pins è deve avè una bassa resistenza è a cunnessione di bassa inductance à a terra per ottene u megliu rendimentu.

U cristallu (XTAL), i dui condensatori di carica (CX1, CX2), è i circuiti interni cunnessi à i pin XTAL1 è XTAL2 formanu l'oscillatore di cristallo 16MHz per u transceiver 2.4GHz. Per ottene a megliu precisione è stabilità di a freccia di riferimentu, deve esse evitata grande capacità parasita. E linee di cristalli duveranu esse dirette u più curtu pussibule è micca in prossimità di i segnali I / O digitale. Questu hè sopratuttu necessariu per i Modi High Data Rate.

U cristallu 32.768 kHz cunnessu à l'oscillatore di cristallo internu di bassa putenza (sub 1µA) furnisce un riferimentu di tempu stabile per tutti i modi di bassa putenza cumprese 32 Bit IEEE 802.15.4 Symbol Counter ("MAC Symbol Counter") è l'applicazione di clock in tempu reale utilizendu l'asincrona. timer T/C2 ("Timer/Counter2 with PWM and Asynchronous Operation").

A capacità di shunt tutale cumpresi CX3, CX4 ùn deve micca più di 15pF in i dui pin.

U currente di furnimentu assai bassu di l'oscillatore richiede un layout attentu di u PCB è ogni percorsu di fuga deve esse evitata.

A diafonia è a radiazione da cambià i segnali digitali à i pin di cristallo o i pin RF ponu degradà u rendiment di u sistema. A prugrammazione di i paràmetri di forza minima di u drive per u signale di output digitale hè cunsigliatu (vede "DPDS0 - Port Driver Strength Register 0").

Table 4-1. Bill of Materials (BoM)

| Designatore | Descrizzione | Valore | U fabricatore | Part Number | Cumentu |

| B1 | Balun SMD

SMD balun / filtru |

2.4 GHz | Wuerth Johanson Technology | 748421245

2450FB15L0001 |

Filtru inclusu |

| CB1 CB3 | LDO VREG

condensatore di bypass |

1 mF (minimu 100 nF) | AVX

Murata |

0603YD105KAT2A GRM188R61C105KA12D | X5R (0603) 10% 16V |

| CB2 CB4 | Condensatore di bypass di l'alimentazione | 1 mF (minimu 100 nF) | |||

| CX1, CX2 | Condensatore di carica di cristalli 16MHz | 12 pF | AVX

Murata |

06035A120JA GRP1886C1H120JA01 | COG (0603) 5% 50V |

| CX3, CX4 | Condensatore di carica di cristalli 32.768kHz | 12 à 25 pF | |||

| C1, C2 | Condensatore di accoppiamentu RF | 22 pF | Epcos Epcos AVX | B37930 B37920

06035A220JAT2A |

C0G 5% 50V (0402 o 0603) |

| C4 (opcional) | Corrispondenza RF | 0.47 pF | Johnstech | ||

| XTAL | Cristalli | CX-4025 16 MHz

SX-4025 16 MHz |

ACAL Taitjen Siward | XWBBPL-F-1 A207-011 | |

| XTAL 32 kHz | Cristalli | Rs = 100 kOhm |

Storia di rivisione

Per piacè nutate chì i numeri di pagina di riferimentu in questa sezione sò riferiti à stu documentu. A rivisione di riferimentu in questa sezione si riferisce à a rivisione di documentu.

Rev. 42073BS-MCU Wireless-09/14

- Cuntenutu invariatu - ricreatu per a liberazione cumminata cù a datasheet.

Rev. 8393AS-MCU Wireless-02/13

- Liberazione iniziale.

© 2014 Atmel Corporation. Tutti i diritti riservati. / Rev.: 42073BS-MCU Wireless-09/14 Atmel®, u logo Atmel è e so cumminazzioni, Enabling Unlimited Possibilities®, è altri sò marchi registrati o marchi di Atmel Corporation o di e so filiali. Altri termini è nomi di prudutti ponu esse marchi di altri.

Disclaimer: L'infurmazioni in stu documentu sò furnite in cunnessione cù i prudutti Atmel. Nisuna licenza, espressa o implicita, per estoppel o altrimenti, à qualsiasi dirittu di pruprietà intellettuale hè cuncessa da stu documentu o in cunnessione cù a vendita di i prudutti Atmel. ECCINU QUELLI STABILITÀ IN I TERMINI E CONDIZIONI DI VENDITA ATMEL SITUATE IN L'ATMEL WEBSITE, ATMEL ASSUME NESSUNA RESPONSABILITÀ E DECLINA QUALSIASI GARANZIA ESPLICITA, IMPLICITA O STATUTARIA RELATIVA A I SO PRODOTTI, INCLUSI, MA NON LIMITATA, A GARANTIA IMPLICITA DI COMMERCIABILITÀ, IDONEITA' PER UN SCOPO NON PARTICULARI, INFRASTRUTTURA. IN NESSUN CASU ATMEL SERA RESPONSABILE PER QUALUNQUE DANNI DIRETTI, INDIRETTI, CONSEGUENTI, PUNITIVI, SPECIALI O INCIDENTALI (INCLUSI, SENZA LIMITAZIONI, DANNI PER PERDITA E PROFITTI, INTERRUPZIONI D'AFFARI O PERDITA D'INFORMAZIONI) RISULTATI DA L'UTILIZZO D'USU. QUESTU DOCUMENTU, ANCHE SI ATMEL HAI AVVISU DI A POSSIBILITÀ DI TALI DANNI. Atmel ùn face alcuna rappresentanza o garanzia in quantu à l'accuratezza o a completezza di u cuntenutu di stu documentu è si riserva u dirittu di fà cambiamenti à e specificazioni è e descrizzioni di i prudutti in ogni mumentu senza avvisu. Atmel ùn hà micca impegnu à aghjurnà l'infurmazioni cuntenute quì. A menu chì specificamente furnitu altrimenti, i prudutti Atmel ùn sò micca adattati è ùn anu micca esse usatu in applicazioni automobilistiche. I prudutti Atmel ùn sò micca destinati, autorizati o garantiti per l'usu cum'è cumpunenti in applicazioni destinate à sustene o sustene a vita.

Mouser Electronics

Distributore Autorizatu

Cliccate à View Prezzi, Inventariu, Consegna è Informazioni di Ciclu di Vita:

ATMEGA644RFR2-ZU

ATMEGA2564RFR2-ZF

ATMEGA644RFR2-ZF

ATMEGA644RFR2-ZUR

ATMEGA1284RFR2-ZU

ATMEGA2564RFR2-ZFR

ATMEGA1284RFR2-ZFR

ATMEGA1284RFR2-ZUR

ATMEGA644RFR2-ZFR

ATMEGA2564RFR2-ZU

ATMEGA1284RFR2-ZF

ATMEGA2564RFR2-ZUR

Assistenza Clienti

Atmel Corporation

1600 Tecnulugia Drive

San Jose, CA 95110

USA

Tel: (+1)408-441-0311

Fax: (+1)408-487-2600

www.atmel.com

Documenti / Risorse

|

Microcontroller Atmel ATmega2564 8bit AVR [pdfManuale di u pruprietariu ATmega2564RFR2, ATmega1284RFR2, ATmega644RFR2, ATmega2564 8bit AVR Microcontroller, ATmega2564, 8bit AVR Microcontroller, AVR Microcontroller, Microcontroller |